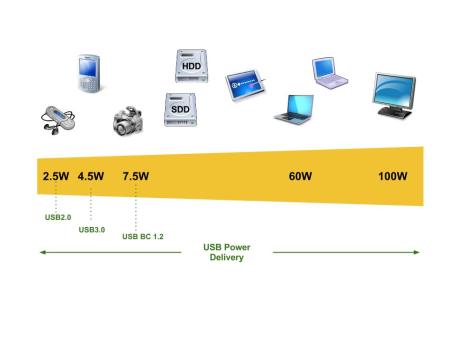

The new USB Power Delivery standard (USB-PD) will enable devices to deliver or sink power over USB cable up to 100W in 6 power profiles. And hopefully it will simplify our life, currently busy with power adapters, battery chargers and connectors. In a previous post of mine, the main features of the USB-PD have been presented.

The new USB Power Delivery standard (USB-PD) will enable devices to deliver or sink power over USB cable up to 100W in 6 power profiles. And hopefully it will simplify our life, currently busy with power adapters, battery chargers and connectors. In a previous post of mine, the main features of the USB-PD have been presented.

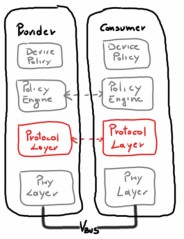

The USB-PD defines a protocol that enable the producer and the consumer device to negotiate the power capabilities and to tailor dinamically the actual power needs. To be compatible with the classic standard USB2.0 and USB3.0, this communication protocol has been specified as a powerline communication (PLC) over VBUS, as depicted in a simplified architecture below. In this configuration the USB-PD PHY in not interfering with the standard communication bus of a USB port and in principle nothing is preventing to have a separate and standalone USB-PD device.

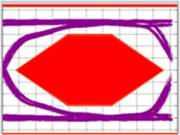

The USB-PD communication protocol is an half-duplex, FSK modulated channel. The frequency carrier is 23.2MHz and the FSK frequency deviation 500KHz. The bit rate is 300 Kbps.

The USB-PD PHY interfaces the VBUS wire only. An inductor is required to isolate the transceiver and the channel from the noisy power supply or load.

The USB-PD standard Specification doesn’t enter in implementation details, but I believe the most probable implementation will use an AC coupling with the VBUS, as depicted above. This approach permits to use low voltage silicon voltage processes, as the capacitor blocks the DC component of the VBUS that can be as high as 20V nominal.

In the above architecture, no mention of the standard USB interface, that it completely separated and independent. It will be interesting to investigate in another post how to protect the VBUS input in case of USB-PD functionality.

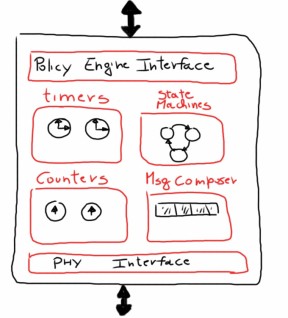

USB-PD PHY (TX)

The TX block receives data to be sent from the upper layer (protocol layer). The functions to be implemented are:

- Receive incoming data from upper layer

- Append the calculated CRC

- 4b5b encode to avoid DC component in the data stream

- Insert preamble and packet delimiters

- FSK Modulator

- VUSB Drive with a bandpass filter

Without enter in implementation details, part of the TX block involves pure digital design. It will be interesting to investigate the implementation of the FSK modulator. The 4b5b encoder avoids DC component in the data stream. The preamble makes the clock synchronization easier and the packet delimiters make the packet sync easier at the RX side.

USB-PD PHY RX

The RX block should receive data on the VBUS and send the payload data to the upper layer (protocol layer). The functions to be implemented are:

- PassBand Filter

- Squelch Detector

- FSK Demodulator

- Extract payload

- 4b5b Decoder

- CRC check

- Data to upper layer

The most interesting part of the RX is the FSK demodulator, as there are many alternative implementations. A coming post will be dedicated to this topic.

The RX squelch detector is requested to minimize the power consumption of the RX block when no data communication on VBUS. The CRC calculation and validation permits to discharge corrupted packets. Only bit-wise correct packet will be delivered to the upper layer (protocol layer).